# 3<sup>rd</sup> ORDER CIC DECIMATION FILTER DESIGN & **IMPLEMENTATION**

# <sup>1</sup>Mir Mohammad Burhan, <sup>2</sup>Nadeem Tariq Beigh, <sup>3</sup>Sandeep Kr. Singh

<sup>1</sup>Student, Sharda University, <sup>2</sup>Student, Sharda University, <sup>3</sup>Assistant Professor, Sharda University <sup>1, 2, 3</sup>Department of Electronics & Communication

<sup>1, 2, 3</sup>Sharda University, Greater Noida, UP, India

Abstract: In this paper the design of 3<sup>rd</sup> order decimation filter with a decimation factor 16 is presented using the FDA tool of DSP system toolbox of MATLAB. The filter is realized using Simulink. The filter is optimized for the size of adders and subtractors in terms of the word length by reducing the word length of consecutive adders to save area and computational complexity. The designed filter is converted to a Verilog RTL using the HDL coder in MATLAB. This filter is implemented in Xilinx and simulated in ISIM simulator for white noise, impulse and step response for 1000 samples. An optimized Verilog RTL implementation of the same filter is also presented. This optimized code is less complex and understandable and has the same functionality with lesser resource utilization.

Index Terms – Decimation filters, CIC filters, Verilog RTL, Filter design, Filter implementation.

#### **I. INTRODUCTION**

Delta-sigma analog-to-digital converters (ADCs) are among the most popular converters that are suitable for low-to-medium speed and high resolution applications such as communications systems, weighing scales and precision measurement applications. These converters use clock oversampling along with noise-shaping to achieve high signal-to-noise ratio (SNR) and, thus, higher effective number of bits (ENOB). Noise-shaping occurs when noise is pushed to higher frequencies that are out of the band of interest. When the out-of-band noise is chopped off, SNR increases. After noise-shaping, the sampling rate is reduced back to its Nyquist rate by means of decimation filters. In fact, deltasigma converters can be partitioned into two main building blocks: modulator and decimation filters. With a good understanding of these building blocks you can arrive at a robust and efficient design. Each of these main building blocks, in turn, is made of several different building blocks themselves. Unlike conventional converters that sample the analog input signal at Nyquist frequency or slightly higher, delta-sigma modulators, regardless of their order, sample the input data at rates that are much higher than Nyquist rate. The oversampling ratio (OSR) usually is expressed in the form of 2m, where m=1, 2, 3... The modulator is an analog block in nature that needs little accuracy in its components. Thus, the burden of design can be pushed onto the decimation filter. The most important role of a decimation filter is to decrease the sampling rate by discarding every few samples. Presented in this article is a quick overview of decimation filters, along with their operation and requirements. Their requirements are based on the order of the delta-sigma modulator used in the converter, along with the overall number of bits being output by the ADC. [2]

#### **II. DIGITAL DECIMATION FILTER**

The decimation filter described in this paper is used in the field of instrumentation. At first, a bit-stream with the rate of 3.2 KHz is generated by a delta-sigma modulator which is over-sampled by 16. Then, the bit-stream passes through a decimation filter, where it is down-sampled to a signal bandwidth of, which has a pass-band ripple of 0.001dB, and the resolution of output is bits. Multiplier takes up most of the chip area and power consumption. But the cascaded-integrator-comb (CIC) filter requires neither multiplier nor coefficient storage, therefore they are widely used in decimation filters.[5]

CIC filter is a very simple digital filter, which is also the Finite Impulse Response (FIR). The transfer function of it is given below:

$$H(z) = \sum_{n=0}^{N-1} z^{-n} = \frac{1 - z^{-n}}{1 - z^{-1}}$$

(1)

The research shows that the stop-band attenuation of CIC filter cannot meet the practical application. How to improve its stop-band attenuation? We can use the modified form of transfer function, which is given below.

$$H(z) = \left(\frac{1}{N} \sum_{n=0}^{N-1} z^{-n}\right)^{k} = \left(\frac{1}{N} \frac{1-z^{-n}}{1-z^{-1}}\right)^{k}$$

(2)

In this function, N is the normalization factor which represents the decimation factor, and K is the CIC filter's order. The stop-band attenuation is fold-increase with K and the edge of pass-band becomes steeper, so the characteristics of the filter become better. In this paper, N=16.

In the CIC filter, K- the order of the transfer function determines the ability of noise suppression at zeros, and it has a certain relation with the output of the modulator. Noise Power Spectrum Density of the modulator is given by (3)

$$N(f) = \hat{e}\sqrt{2\tau}(2\sin(\pi f\tau))^{L}, 0 \le f \le f_{0}$$

(3)

L represents the modulator's order and  $\tau$  represents the sampling period of the analog modulator, and  $\hat{e}$  represents quantization error. If the order of the CIC filter, K, is equal to the order of the modulator, L, the Noise Power Spectrum Density of the signal that output of the CIC filter is shown by (4)

$$N(f) = \hat{e}\sqrt{2N\tau}(2\sin(\pi f\tau))^L, 0 \le f \le f_0$$

(4)

If K=L+1, the Noise Power Spectrum Density of the signal that output of the CIC filter is given by (5)

$$N(f) = \hat{e}\sqrt{2N\tau}(2\sin(\pi f\tau))^{L}\frac{\operatorname{sinc}(f\tau)}{\operatorname{sinc}(Kf\tau)}, 0 \le f \le f_{0}$$

(5)

# © 2018 JETIR May 2018, Volume 5, Issue 5

#### www.jetir.org (ISSN-2349-5162)

Compare with (3), (4) and (5), it is not difficult to find that the change of Noise Power Spectrum Density after the down-sample by CIC filter is very small when K=L+1. From (5), we can find that with the increase of K, the performance of the output signal becomes better, but it will make hardware consumption largely increased. So we make K=L+1=3 in our design. The transfer function is given below. [3]

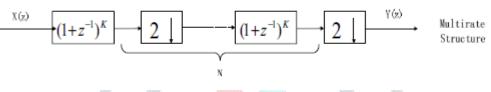

Fig.1: Hongernauer decimation filter.[4]

$$H(z) = \left(\frac{1}{16} \sum_{n=0}^{15} z^{-n}\right)^3 = \left(\frac{1}{16} \frac{1-z^{-16}}{1-z^{-1}}\right)^3 \tag{6}$$

A proper structure can effectively reduce the power consumption and area. As we studied, there are four popular structures [1]. Figure 2 presents the more efficient structures, which are Hongernauer CIC structure and multi-rate structure. They have different advantages. For example, the advantage of the first one is when over-sampling rate grows up area will change with it; and the advantage of the second one is when the over-sampling rate grows up and the word length becomes small, the power consumption will be down, in this paper, we use Hongernauer CIC structure.[6]

Fig.2: Multi rate structure.[4]

#### **III. DESIGN OF DECIMATION FILTER**

In this paper the 3<sup>rd</sup> order CIC decimator with a decimation factor of 16 is presented. The filter is designed using MATLAB Simulink FDA tool and implemented using Verilog RTL. The designed filter is compared with another CIC Verilog implementation for resource utilization. Given below is the parameter specification of the filter designed using the Simulink FDA tool. The Verilog code for the filter is given in Appendix. The Frequency – Phase response and the Pole-Zero plot is given below as obtaoned from the FDA tool.

| Parameter                       | Value                    |

|---------------------------------|--------------------------|

| Filter Structure                | Cascaded Integrator Comb |

| Decimation factor               | 16                       |

| Differential Delay              |                          |

| Number of sections              | 3                        |

| Stable                          | Yes                      |

| Linear Phase                    | Yes (Type 2)             |

| Number of Multipliers           | 0                        |

| Number of Adders                | 6                        |

| Number of States                | 6                        |

| Multiplicatins per input sample | 0                        |

| Additions per input sample      | 3.186                    |

| Sampling Frequency              | 3.2Khz                   |

| Wordlengths                     | [21 20 19 19 17 16]      |

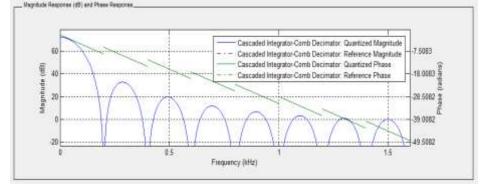

Fig.3: Frequency – Phase response of the filter

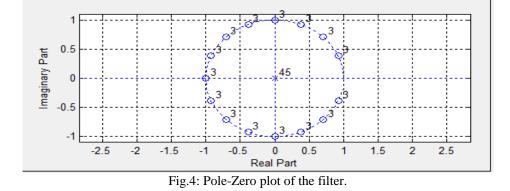

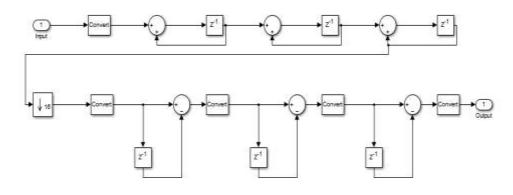

It can be seen that the pass band gain of the filter is around 70 dB and the phase is linear over this region with a range of -6 to -20 degrees. The PZ plot has all zeros on the unit circle with a poles at the origin. The generated Simulink model is given below with three integrators and three differentiators connected with a down sample switch of 16. [8]

| 738.527 ns         Name       Value         > Marce       Value         > Marce       1191         > Marce       10,833         10,833       1191,8,0,0,8,7700,29016,32480,20850,1754,65088,50836,34630,34688,35712,36736,37760,3878,39808,40832,418         Marce       1         Marce       1         Marce       1         Marce       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| image: state in the state                                 |

| image: state in the state                                 |

| Image: Construction of the second sec               |

| Ib ck_enable     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| reset o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $rac{1}{2}$ $ ightarrow$ $ igh$ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| X1: 738.527 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Fig.6: Simulation output.

Fig.7: Technology Schematics.

| Table 2: Synthesis I    | Report.               | Table 3: Design Statistics |               |     |       |                   |

|-------------------------|-----------------------|----------------------------|---------------|-----|-------|-------------------|

| Adders/Subtractors      | 6                     |                            | IOs           | 36  |       | IO Buffers        |

| 17-bit subtractor       | 1                     |                            | Cell Usage    |     |       | IBUF              |

| 18-bit subtractor       | 1                     |                            | BELS          |     | 1     | OBUF              |

| 20-bit adder            | 1                     |                            | AND2          | 206 |       |                   |

| 20-bit subtractor       | 1                     | 1                          | AND3          | 7   |       |                   |

| 21-bit adder            | 1                     |                            | AND4          | 1   |       |                   |

| 22-bit adder            | 1                     | 5                          | INV           | 136 |       |                   |

| Counters                | 1                     | 27                         | OR2           | 197 |       |                   |

| 4-bit up counter        | 1                     | 1 100                      | OR3           | 6   |       |                   |

| Registers               | 3                     |                            | XOR2          | 217 | 6     |                   |

| Flip-Flops              | 3                     | 1                          | Flip          |     |       |                   |

| An optimized decimation | filter code is presen | ted in                     | Flops/Latches |     | Appen | dix, with the sim |

| Annendix | with | the | simulation | output |

|----------|------|-----|------------|--------|

12 17

An optimized decimation filter code is presented in and other parameters given below.

|                    |       |               |          |          |          |                                                |          | 1,249.027 r | 15       |

|--------------------|-------|---------------|----------|----------|----------|------------------------------------------------|----------|-------------|----------|

| Name               | Value |               | 1,160 ns | 1,180 ns | 1,200 ns | 1,220 ns                                       | 1,240 ns |             | 1,260 ns |

| 🕞 😽 DWord_ro[15:0] | 2004  | 2061          | 2084     | X 17     | 25 X     | 1716                                           |          | 200         | 4        |

| 🗓 DSM_i            | 0     | ۰.۸۸          |          |          |          |                                                |          |             |          |

| U DSM_clk_i        | 0     |               |          |          |          | <u>, 1000000000000000000000000000000000000</u> |          |             | 00000    |

| U WordClk_i        | 1     |               |          |          |          |                                                |          |             |          |

| 🐌 Reset_i          | 0     |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       |               |          |          |          |                                                |          |             |          |

|                    |       | X1: 1,249.027 | ns       |          |          |                                                |          |             |          |

FDC

FDCE

1

176

Fig. 8: Output Simulation of optimized filter.

Fig.9: Technology schematics of optimized filter.

| Table 4: Syn       | thesis Report. | -   | Table 5: Design statistics |    |

|--------------------|----------------|-----|----------------------------|----|

| Adders/Subtractors | 6              | 1   | IOs                        | 12 |

| 17-bit subtractor  | 1              | 15  | Cell Usage<br>BELS         |    |

| 18-bit subtractor  | 1              |     | AND2                       | 13 |

| 20-bit adder       | 1              |     | AND8                       | 1  |

| 20-bit subtractor  | 1              | 1   | INV                        | 2  |

| 21-bit adder       | 1              | 100 | XOR2                       | 14 |

| 22-bit adder       | 1              |     | XOR2                       | 14 |

| Counters           | 1              | ·   | Flip Flops/Latches         |    |

| 4-bit up counter   | 1              | 1   | FDC<br>IO Buffers          | 16 |

| Tristates          | 1              |     | IBUF                       | 4  |

| 8-bit Tristates    | 1              |     | OBUFE                      | 8  |

#### **IV. CONCLUSION**

In this paper the design of 3<sup>rd</sup> order decimation filter with a decimation factor 16 was presented using the FDA tool of DSP system toolbox of MATLAB. The filter was realized using Simulink. The filter was optimized for the size of adders and subtractors in terms of the word length by reducing the word length of consecutive adders to save area and computational complexity. The designed filter was converted to a Verilog RTL using the HDL coder in MATLAB. This filter was implemented in Xilinx and simulated in ISIM simulator for white noise, impulse and step reponse for 1000 samples. An optimized Verilog RTL implementation of the same filter was also presented. This optimized code is less complex and understandable and has the same functionality with lesser resource utilization as verified by the tables given above. The area utilization in terms of I/O buffers is 1/3<sup>rd</sup> .the cell usage reduces considerably aby an amount of around 600.Ths reducing the area by about 64%.This shows that the MATLAB generated HDL code is less efficient as compared to the presented code.

#### REFERENCES

- [1] Bibin John, Fabian Wagner and Wolfgang H. Krautschneider, 2010. "Comparison of Decimation Filter Architectures for a Sigma-Delta Analog to Digital Converter", TUHH Telematics.

- [2] Arash loloee, 2014. "Exploring Decimation Filters", Journal of High Frequency Electronics", 31-40.

- [3] Kiran Agarwal Gupta, Tejashree Patil, 2017. "Low Pass Reconfigurable Decimation Filter Architecture for 3.8 MHz Frequency", 2nd IEEE International Conference on Recent Trends in Electronics Information & Communication Technology (RTEICT) India.

- [4] Karuna Grover, Rajesh Mehra, Chandani, 2017. "FPGA Based Decimator Using Fully Parallel Technique for Hearing Aid Applications", 3rd IEEE International Conference on "Computational Intelligence and Communication Technology".

- [5] Ricardo Garcia Baez, Gordana Jovanovic Dolecek, 2016. "Modified Comb Decimation Filter: Design and Implementation", IEEE 59th International Midwest Symposium on Circuits and Systems (MWSCAS) Abu Dhabi UAE.

- [6] YongSheng Wang, YaQin Ru, Yang Liu, Xiao Zhou, Shan Li, Bei Cao, XiaoWei Liu, 2016. "An Area-Efficient Multi-Bit Sigma-Delta modulator", IEEE.

- [7] Latha Raja Gopal, 2016. "Power and Area Efficient Decimation Filter Architectures of Wireless Receivers", Springer.

- [8] Nasir Nabi Hurrah, Zubair Jan, Anil Bhardwaj, Shabir Ahmad Parah, Amit Kant Pandit, 2015. "Oversampled Sigma Delta ADC Decimation Filter: Design Techniques, Challenges, Trade-offs and Optimization", Proceedings of 2015 RAECS UIET Panjab University Chandigarh 21-22nd December 2015.

- [9] K.Shanthi, Dr.B.K.Madhavi, 2015. "Implementation of Optimized Cascaded Integrator Comb Filters for Digital Up, Down Conversions", International Journal of Science Engineering and Technology Research (IJSETR), Vol 4, Issue 7.

- [10] Sudhir Rao Rupanagudi, Varsha G. Bhat, Hemalatha S.G., Bhavana N., Archana M., Chandrika B. V., Ashwini R., Keerti G. Torvi, Darshan S. R., Abhilash B.G., Anil K.S., Vinayak Swamy K. M, 2014. "Design of a Low Power Digital Down Converter for 802.16m – 4G WiMAX on FPGA", International Conference on Advances in Computing, Communications and Informatics (ICACCI).

### © 2018 JETIR May 2018, Volume 5, Issue 5

[11] Suraj R. Gaikwad, Gopal S. Gawande, 2014." Design and Implementation of Efficient FIR Filter Structures using Xilinx System Generator", International Journal of scientific research and management (IJSRM).

# APPENDIX

### Verilog RTL code of CIC decimation filter designed by MATLAB HDL Coder.

MODULE DECIMATION\_16 CLK, CLK\_ENABLE, RESET, FILTER\_IN, FILTER\_OUT, CE OUT INPUT CLK; INPUT CLK\_ENABLE; INPUT RESET; INPUT SIGNED [15:0] FILTER\_IN; //SFIX16\_EN15 OUTPUT SIGNED [15:0] FILTER\_OUT; OUTPUT CE\_OUT; //MODULE ARCHITECTURE: DECIMATION\_16 REG [3:0] CUR\_COUNT; // UFIX4 WIRE PHASE\_1; // BOOLEAN WIRE CE\_DELAYLINE; // BOOLEAN REG INT\_DELAY\_PIPE [0:1]; // BOOLEAN WIRE CE\_GATED; // BOOLEAN REG CE\_OUT\_REG; // BOOLEAN REG SIGNED [15:0] INPUT\_REGISTER; // SFIX16\_EN15 // -- SECTION 1 SIGNALS WIRE SIGNED [15:0] SECTION\_IN1; // SFIX16\_EN15 WIRE SIGNED [20:0] SECTION\_CAST1; // SFIX21\_EN8 WIRE SIGNED [20:0] SUM1; // SFIX21\_EN8 REG SIGNED [20:0] SECTION\_OUT1; // SFIX21\_EN8 WIRE SIGNED [20:0] ADD\_CAST; // SFIX21\_EN8 WIRE SIGNED [20:0] ADD\_CAST\_1; // SFIX21\_EN8 WIRE SIGNED [21:0] ADD\_TEMP; // SFIX22\_EN8 // -- SECTION 2 SIGNALS WIRE SIGNED [20:0] SECTION\_IN2; // SFIX21\_EN8 WIRE SIGNED [19:0] SECTION\_CAST2; // SFIX20\_EN7 WIRE SIGNED [19:0] SUM2; // SFIX20\_EN7 REG SIGNED [19:0] SECTION\_OUT2; // SFIX20\_EN7 WIRE SIGNED [19:0] ADD\_CAST\_2; // SFIX20\_EN7 WIRE SIGNED [19:0] ADD\_CAST\_3; // SFIX20\_EN7 WIRE SIGNED [20:0] ADD\_TEMP\_1; // SFIX21\_EN7 // -- SECTION 3 SIGNALS WIRE SIGNED [19:0] SECTION\_IN3; // SFIX20\_EN7 WIRE SIGNED [18:0] SECTION\_CAST3; // SFIX19\_EN6 WIRE SIGNED [18:0] SUM3; // SFIX19\_EN6 REG SIGNED [18:0] SECTION\_OUT3; // SFIX19\_EN6 WIRE SIGNED [18:0] ADD\_CAST\_4; // SFIX19\_EN6 WIRE SIGNED [18:0] ADD\_CAST\_5; // SFIX19\_EN6 WIRE SIGNED [19:0] ADD\_TEMP\_2; // SFIX20\_EN6 // -- SECTION 4 SIGNALS WIRE SIGNED [18:0] SECTION\_IN4; // SFIX19\_EN6 REG SIGNED [18:0] DIFF1; // SFIX19\_EN6 WIRE SIGNED [18:0] SECTION\_OUT4; // SFIX19\_EN6 WIRE SIGNED [18:0] SUB\_CAST; // SFIX19\_EN6 WIRE SIGNED [18:0] SUB\_CAST\_1; // SFIX19\_EN6 WIRE SIGNED [19:0] SUB\_TEMP; // SFIX20\_EN6 REG SIGNED [18:0] CIC\_PIPELINE4; // SFIX19\_EN6 // -- SECTION 5 SIGNALS WIRE SIGNED [18:0] SECTION\_IN5; // SFIX19\_EN6 WIRE SIGNED [16:0] SECTION\_CAST5; // SFIX17\_EN4 REG SIGNED [16:0] DIFF2; // SFIX17\_EN4 WIRE SIGNED [16:0] SECTION\_OUT5; // SFIX17\_EN4 WIRE SIGNED [16:0] SUB\_CAST\_2; // SFIX17\_EN4 WIRE SIGNED [16:0] SUB\_CAST\_3; // SFIX17\_EN4 WIRE SIGNED [17:0] SUB\_TEMP\_1; // SFIX18\_EN4 REG SIGNED [16:0] CIC\_PIPELINE5; // SFIX17\_EN4 -- SECTION 6 SIGNALS WIRE SIGNED [16:0] SECTION\_IN6; // SFIX17\_EN4 WIRE SIGNED [15:0] SECTION\_CAST6; // SFIX16\_EN3 REG SIGNED [15:0] DIFF3; // SFIX16\_EN3 WIRE SIGNED [15:0] SECTION\_OUT6; // SFIX16\_EN3 WIRE SIGNED [15:0] SUB\_CAST\_4; // SFIX16\_EN3 WIRE SIGNED [15:0] SUB\_CAST\_5; // SFIX16\_EN3 WIRE SIGNED [16:0] SUB\_TEMP\_2; // SFIX17\_EN3 REG SIGNED [15:0] OUTPUT\_REGISTER; // SFIX16\_EN3 --- CE OUTPUT GENERATION ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: CE OUTPUT IF (RESET == 1'B1) BEGIN CUR\_COUNT <= 4'B0000;

```

END

ELSE BEGIN

IF (CLK_ENABLE == 1'B1) BEGIN

IF (CUR_COUNT == 4'B1111) BEGIN

CUR_COUNT <= 4'B0000;

END

ELSE BEGIN

CUR_COUNT <= CUR_COUNT + 1;

END

END

END

END // CE_OUTPUT

ASSIGN PHASE_1 = (CUR_COUNT == 4'B0001 && CLK_ENABLE ==

1'B1)? 1:0;

ALWAYS @ (POSEDGE CLK OR POSEDGE RESET)

BEGIN: CE_DELAY

IF (RESET == 1'B1) BEGIN

INT_DELAY_PIPE [0] <= 1'B0;

INT_DELAY_PIPE [1] <= 1'B0;

END

ELSE BEGIN

IF (PHASE_1 == 1'B1) BEGIN

INT_DELAY_PIPE [1] <= INT_DELAY_PIPE [0];

INT_DELAY_PIPE [0] <= CLK_ENABLE;

END

END

END // CE_DELAY

ASSIGN CE_DELAYLINE = INT_DELAY_PIPE [1];

ASSIGN CE_GATED = CE_DELAYLINE & PHASE_1;

----- CE OUTPUT REGISTER ------

ALWAYS @ (POSEDGE CLK OR POSEDGE RESET)

BEGIN: CE_OUTPUT_REGISTER

IF (RESET == 1'B1) BEGIN

CE_OUT_REG <= 1'B0;

END

ELSE BEGIN

CE_OUT_REG <= CE_GATED;

END

END // CE_OUTPUT_REGISTER

----- INPUT REGISTER -

ALWAYS @ (POSEDGE CLK OR POSEDGE RESET)

BEGIN: INPUT_REG_PROCESS

IF (RESET == 1'B1) BEGIN

INPUT_REGISTER <= 0;

END

ELSE BEGIN

IF (CLK_ENABLE == 1'B1) BEGIN

INPUT_REGISTER <= FILTER_IN;

END

END

END // INPUT_REG_PROCESS

----- SECTION # 1: INTEGRATOR ------

ASSIGN SECTION_IN1 = INPUT_REGISTER;

ASSIGN SECTION_CAST1 = $SIGNED ({{12{SECTION_IN1 [15]}}},

SECTION_IN1 [15:7]});

ASSIGN ADD_CAST = SECTION_CAST1;

ASSIGN ADD_CAST_1 = SECTION_OUT1;

ASSIGN ADD_TEMP = ADD_CAST + ADD_CAST_1;

ASSIGN SUM1 = ADD_TEMP [20:0];

ALWAYS @ (POSEDGE CLK OR POSEDGE RESET)

BEGIN: INTEGRATOR_DELAY_SECTION1

IF (RESET == 1'B1) BEGIN

SECTION_OUT1 <= 0;

END

ELSE BEGIN

IF (CLK_ENABLE == 1'B1) BEGIN

SECTION_OUT1 <= SUM1;

END

END

END // INTEGRATOR_DELAY_SECTION1

--- SECTION # 2: INTEGRATOR

ASSIGN SECTION IN2 = SECTION OUT1;

ASSIGN SECTION_CAST2 = SECTION_IN2 [20:1];

ASSIGN ADD_CAST_2 = SECTION_CAST2;

```

# © 2018 JETIR May 2018, Volume 5, Issue 5

ASSIGN ADD\_CAST\_3 = SECTION\_OUT2; ASSIGN ADD\_TEMP\_1 = ADD\_CAST\_2 + ADD\_CAST\_3; ASSIGN SUM2 = ADD\_TEMP\_1 [19:0]; ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: INTEGRATOR\_DELAY\_SECTION2 IF (RESET == 1'B1) BEGIN SECTION\_OUT2 <= 0; END ELSE BEGIN IF (CLK\_ENABLE == 1'B1) BEGIN SECTION\_OUT2 <= SUM2; END END END // INTEGRATOR\_DELAY\_SECTION2 // ----- SECTION # 3: INTEGRATOR ------ASSIGN SECTION\_IN3 = SECTION\_OUT2; ASSIGN SECTION\_CAST3 = SECTION\_IN3 [19:1]; ASSIGN ADD\_CAST\_4 = SECTION\_CAST3; ASSIGN ADD\_CAST\_5 = SECTION\_OUT3; ASSIGN ADD\_TEMP\_2 = ADD\_CAST\_4 + ADD\_CAST\_5; ASSIGN SUM3 = ADD\_TEMP\_2 [18:0]; ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: INTEGRATOR\_DELAY\_SECTION3 IF (RESET == 1'B1) BEGIN SECTION\_OUT3 <= 0; END ELSE BEGIN IF (CLK\_ENABLE == 1'B1) BEGIN SECTION\_OUT3 <= SUM3; END END END // INTEGRATOR\_DELAY\_SECTION3 // ----- SECTION # 4: COMB -ASSIGN SECTION\_IN4 = SECTION\_OUT3; ASSIGN SUB\_CAST = SECTION\_IN4; ASSIGN SUB\_CAST\_1 = DIFF1; ASSIGN SUB\_TEMP = SUB\_CAST - SUB\_CAST\_1; ASSIGN SECTION\_OUT4 = SUB\_TEMP [18:0]; ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: COMB\_DELAY\_SECTION4 IF (RESET == 1'B1) BEGIN DIFF1  $\leq 0$ ; END ELSE BEGIN IF (PHASE 1 == 1'B1) BEGIN DIFF1 <= SECTION\_IN4; END END END // COMB\_DELAY\_SECTION4 ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: CIC\_PIPELINE\_PROCESS\_SECTION4 IF (RESET == 1'B1) BEGIN CIC\_PIPELINE4 <= 0; END ELSE BEGIN IF (PHASE\_1 == 1'B1) BEGIN CIC\_PIPELINE4 <= SECTION\_OUT4; END END END // CIC\_PIPELINE\_PROCESS\_SECTION4 // ----- SECTION # 5: COMB ----ASSIGN SECTION\_IN5 = CIC\_PIPELINE4; Verilog RTL code for the optimized decimation filter MODULE SINC\_IMLEMENTATION (

MODULE SINC\_INILIALITATION ( DSM\_I, DSM\_CLK\_I, WORDCLK\_I, RESET\_I, DWORD\_RO); INPUT DSM\_CLK\_I; // DSM-RATE CLOCK (BIT CLOCK) INPUT WORDCLK\_I; // OUTPUT WORD-RATE CLOCK INPUT RESET\_I; // ACTIVE-HI RESET INPUT DSM\_I; // INPUT FROM MODULATOR OUTPUT [15:0] DWORD\_RO; // 16-BIT OUTPUT WORD REG [20:0] ACC1\_R; REG [19:0] ACC2\_R; REG [18:0] ACC3\_R; REG [18:0] ACC3\_Q2\_R; REG [18:0] DIFF1\_R; REG [16:0] DIFF2\_R; REG [15:0] DIFF3\_R; REG [18:0] DIFF1\_Q1\_R;

REG [16:0] DIFF2\_Q2\_R; REG [15:0] DWORD\_RO; REG [15:0] TEMP;

### www.jetir.org (ISSN-2349-5162)

ASSIGN SECTION\_CAST5 = SECTION\_IN5 [18:2]; ASSIGN SUB\_CAST\_2 = SECTION\_CAST5; ASSIGN SUB\_CAST\_3 = DIFF2; ASSIGN SUB\_TEMP\_1 = SUB\_CAST\_2 - SUB\_CAST\_3; ASSIGN SECTION\_OUT5 = SUB\_TEMP\_1 [16:0]; ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: COMB\_DELAY\_SECTION5 IF (RESET == 1'B1) BEGIN DIFF2  $\leq = 0$ : END ELSE BEGIN IF (PHASE\_1 == 1'B1) BEGIN DIFF2 <= SECTION\_CAST5; END END END // COMB\_DELAY\_SECTION5 ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: CIC\_PIPELINE\_PROCESS\_SECTION5 IF (RESET == 1'B1) BEGIN CIC\_PIPELINE5 <= 0; END ELSE BEGIN IF (PHASE\_1 == 1'B1) BEGIN CIC\_PIPELINE5 <= SECTION\_OUT5; END END END // CIC\_PIPELINE\_PROCESS\_SECTION5 ----- SECTION # 6: COMB ----ASSIGN SECTION\_IN6 = CIC\_PIPELINE5; ASSIGN SECTION\_CAST6 = SECTION\_IN6 [16:1]; ASSIGN SUB\_CAST\_4 = SECTION\_CAST6; ASSIGN SUB\_CAST\_5 = DIFF3; ASSIGN SUB\_TEMP\_2 = SUB\_CAST\_4 - SUB\_CAST\_5; ASSIGN SECTION\_OUT6 = SUB\_TEMP\_2 [15:0]; ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: COMB\_DELAY\_SECTION6 IF (RESET == 1'B1) BEGIN DIFF3 <= 0; END ELSE BEGIN IF (PHASE\_1 == 1'B1) BEGIN DIFF3 <= SECTION\_CAST6; END END END // COMB\_DELAY\_SECTION6 ----- OUTPUT REGISTER ------11 ALWAYS @ (POSEDGE CLK OR POSEDGE RESET) BEGIN: OUTPUT\_REG\_PROCESS IF (RESET == 1'B1) BEGIN OUTPUT\_REGISTER <= 0; END ELSE BEGIN IF (PHASE\_1 == 1'B1) BEGIN OUTPUT\_REGISTER <= SECTION\_OUT6; END END END // OUTPUT\_REG\_PROCESS // ASSIGNMENT STATEMENTS ASSIGN CE\_OUT = CE\_OUT\_REG; ASSIGN FILTER\_OUT = OUTPUT\_REGISTER; ENDMODULE // DECIMATION 16 //REG [7:0] WORD\_COUNT; // INTERNAL WIRES // 2'S-COMP VERSION OF DWORD WIRE [20:0] DWORD\_2COMP\_W; // SINC FILTER ASSIGN DWORD\_2COMP\_W = (DSM\_I==1'B0)? 21'D0: 21'D1; // ACCUMULATOR (INTEGRATOR) ALWAYS @ (NEGEDGE DSM\_CLK\_I OR POSEDGE RESET\_I) BEGIN IF (RESET\_I) BEGIN /\* INITIALIZE ACC REGISTERS ON RESET\_I \*/ ACC1\_R<=21'D0; ACC2\_R<=20'D0; ACC3\_R<=19'D0; END ELSE BEGIN /\* PERFORM ACCUMULATION PROCESS \*/

726

ACC1\_R<=ACC1\_R + DWORD\_2COMP\_W; ACC2\_R<=ACC2\_R + ACC1\_R; ACC3\_R<=ACC3\_R + ACC2\_R; END END

```

//

// DIFFERENTIATOR AND DECIMATION

//

ALWAYS @ (POSEDGE WORDCLK_I OR POSEDGE RESET_I)

BEGIN

IF (RESET_I)

BEGIN

ACC3_Q2_R<=19'D0;

DIFF1_Q1_R<=19'D0;

DIFF2_Q2_R<=17'D0;

DIFF1_R<=19'D0;

DIFF2_R<=17'D0;

DIFF3_R<=16'D0;

TEMP<=16'D0;

END

ELSE

BEGIN

DIFF1_R<= ACC3_R - ACC3_Q2_R;

DIFF2_R<=DIFF1_R - DIFF1_Q1_R;

DIFF3_R<=DIFF2_R - DIFF2_Q2_R;

DIFF3_R<=DIFF2_R - DIF

ACC3_Q2_R<=ACC3_R;

DIFF1_Q1_R<=DIFF1_R;

DIFF2_Q2_R<=DIFF2_R;

TEMP<=DIFF3_R;

DWORD_RO<=TEMP;

END

END

ENDMODULE

```